Accelerator on a Chip

/Accelerator on a Chip

In 1927, Rolf Wideroe pioneered the building of the first linear particle accelerators based on synchronous acceleration. An ac signal and its inverse are alternatively directly coupled to a series of tubes in a vacuum. At the peak voltage difference particles enter the gap between the tubes and are accelerated by the electric field potential. While inside the tubes, the particles are shielded and drift. Each gap adds more energy equal to the voltage difference seen by the particles.

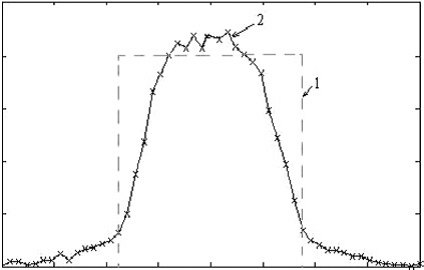

This animation shows a particle emitted from source S with some initial velocity U0. Each gap adds another voltage gain. In our case, the initial velocity is 5eV and the gap potential field is +-8v or 16V. in this example our particle (either a proton or a deuteron) would have 5 + 4*16 or 69eV on exit from C4. As the particle gains velocity, each subsequent drift tube must be longer. To accelerate a proton to 3.5Kev would require 220 stages and with a 1GHz clock would be 60.5mm long.

If the voltage is increased, fewer stages are needed to get to 3.5Kev, but the power increases with the square of the voltage. If the frequency is increased, each stage is shorter, but the power is linearly increased. In this case a 1GHz clock results in a 60.5mm long accelerator but a 2GHz clock is only 32mm long.

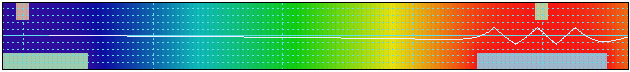

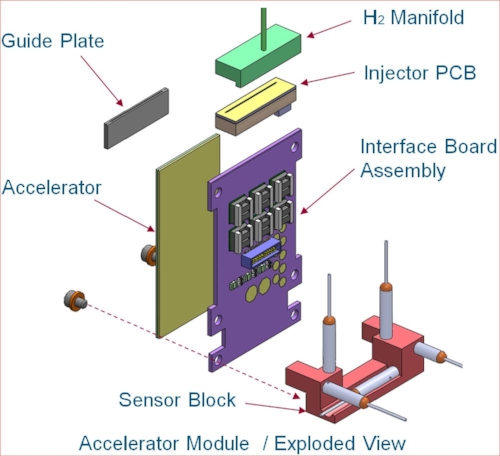

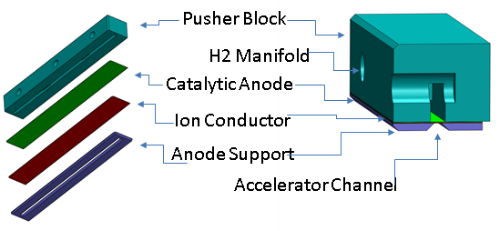

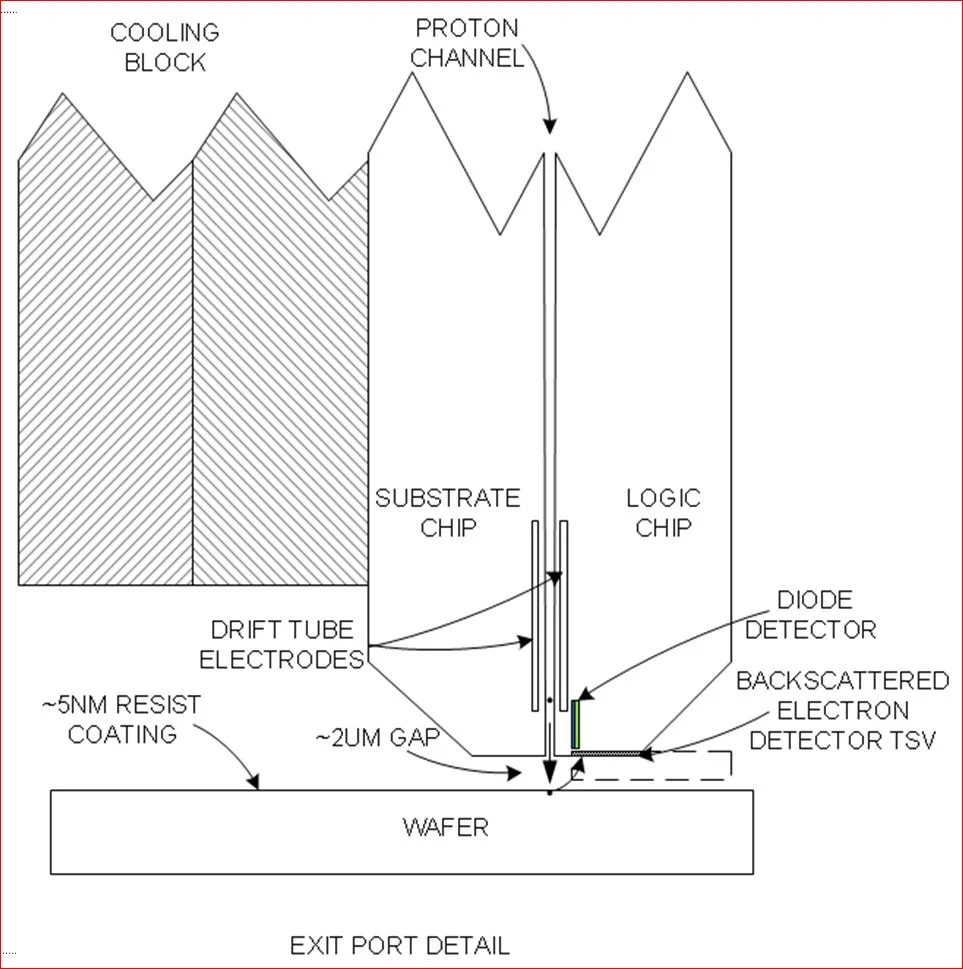

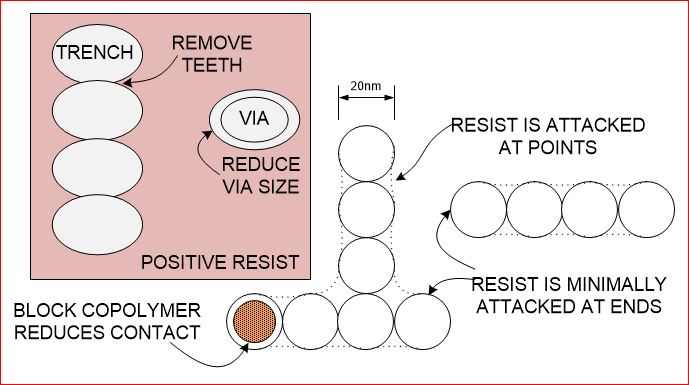

To integrate a linear accelerator into a silicon chip, a 50nm wide by 50nm deep trench is etched into a dielectric layer (silicon dioxide) on a silicon wafer called the channel substrate.

The channel wafer can be bonded to another wafer to form a closed channel. This second wafer contains the drive and control electronics and is called the logic chip. Metal patterns orthogonal to these channels are embedded in the dielectric and form the drift tube electrodes. These electrodes are connected to the drive circuitry with through silicon vias E1 and E2.

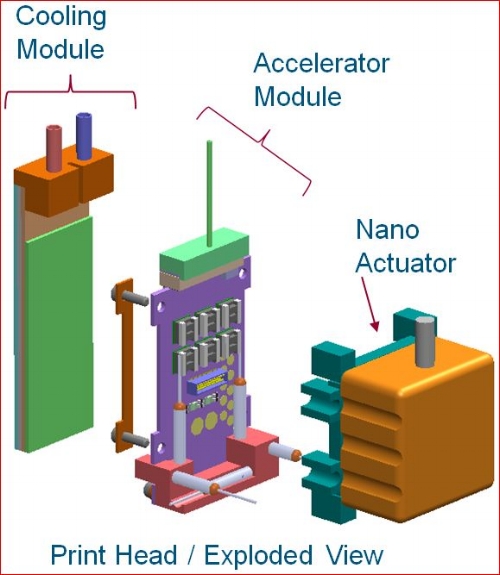

The bonded channel substrate and the logic chip form the accelerator module. In order to sweep as large an area as possible, In order to write as wide a path as possible, 262,144 (2^18) accelerator channels are etched on a 100nm pitch. This allows at least 254,000 active accelerators per head after allowing some overlay for aligning head to head and gives an inch wide path per head. See The Print Head next.